Price and Delivery

When the Terasic DE25-Standard Development and Education Kit was revealed some time ago, it appeared to be a strong contender as a follow-up to the MiSTer FPGA DE10-Nano project. Not exactly a MiSTer 2, but more of a MiSTer Pro or 1.5. The main issue with the DE25 board was the price, at $586 standard or $415 with an academic discount.

The community had been waiting for the Nano variant, which was revealed a few weeks ago, although no price was announced at the time. The price has now been confirmed at $248 standard, or $215 with an academic discount. The DE25-Nano is expected to ship in October or November and is already available to purchase.

Don’t Go Rushing to Buy One Yet

Even though the pricing appears to be very reasonable, don’t rush out to buy one just yet. The DE25-Nano would need to be adopted by the community, and the MiSTer framework would need to be ported to the new hardware, which in itself can bring challenges. However, if it does gain community support, this board could potentially improve existing cores and open up the possibility of additional ones being brought to FPGA gaming. Either way, exciting times lie ahead.

Check out the information for yourself on terasic’s website. Some which can be found below.

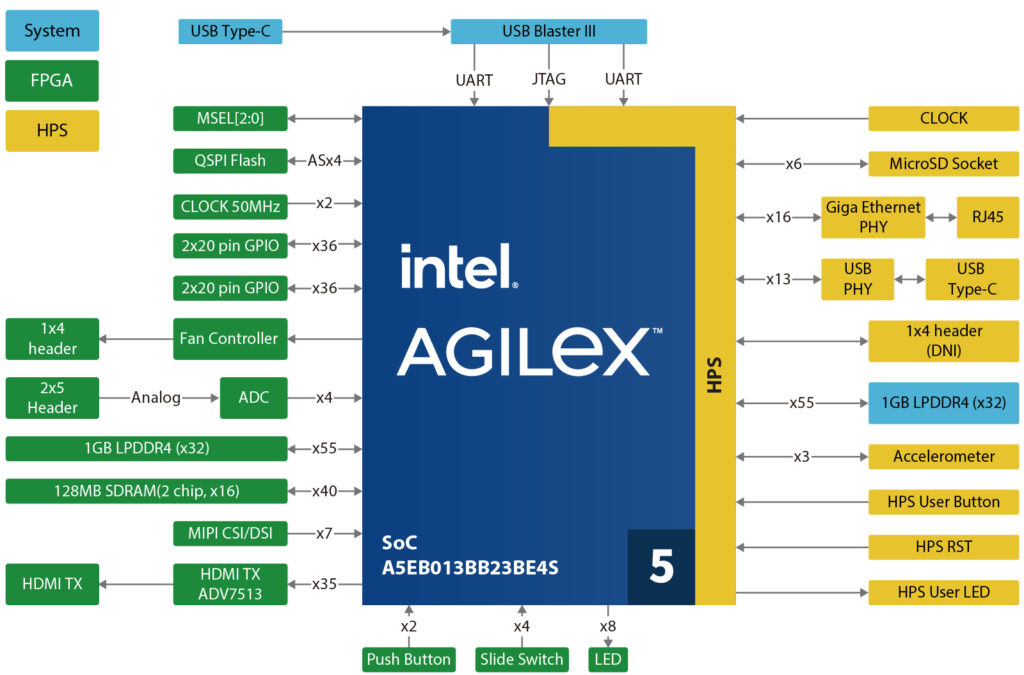

DE25-Nano

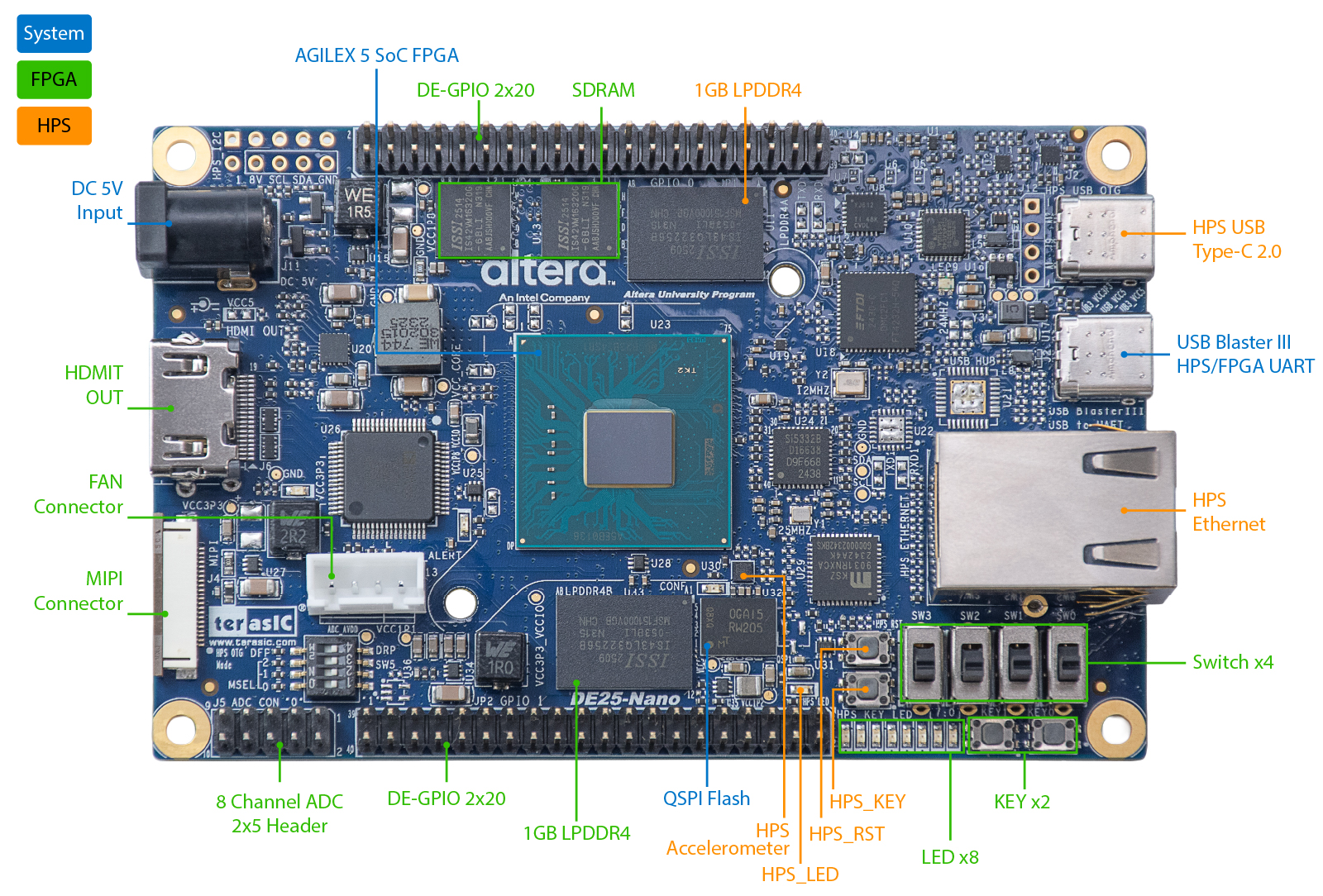

- FPGA: A5EB013BB23BE4SR1 (138K Logic Elements)

- Dimensions: 106.9 mm x 68.58mm

- Onboard Programmer: USB-Blaster III via USB Type-C connector

- Configuration Mode: Supports ASx4 mode with 128 Mbit QSPI Flash

- Cooling Solution: Active heatsink

FPGA side

- LPDDR4: 1GB LPDDR4 with 32-bit data bus. Data Rate: 2133 MT/s.

- SDRAM: 128MB SDRAM with 16-bit data bus

- HDMI Output: Supports up to 1080p resolution

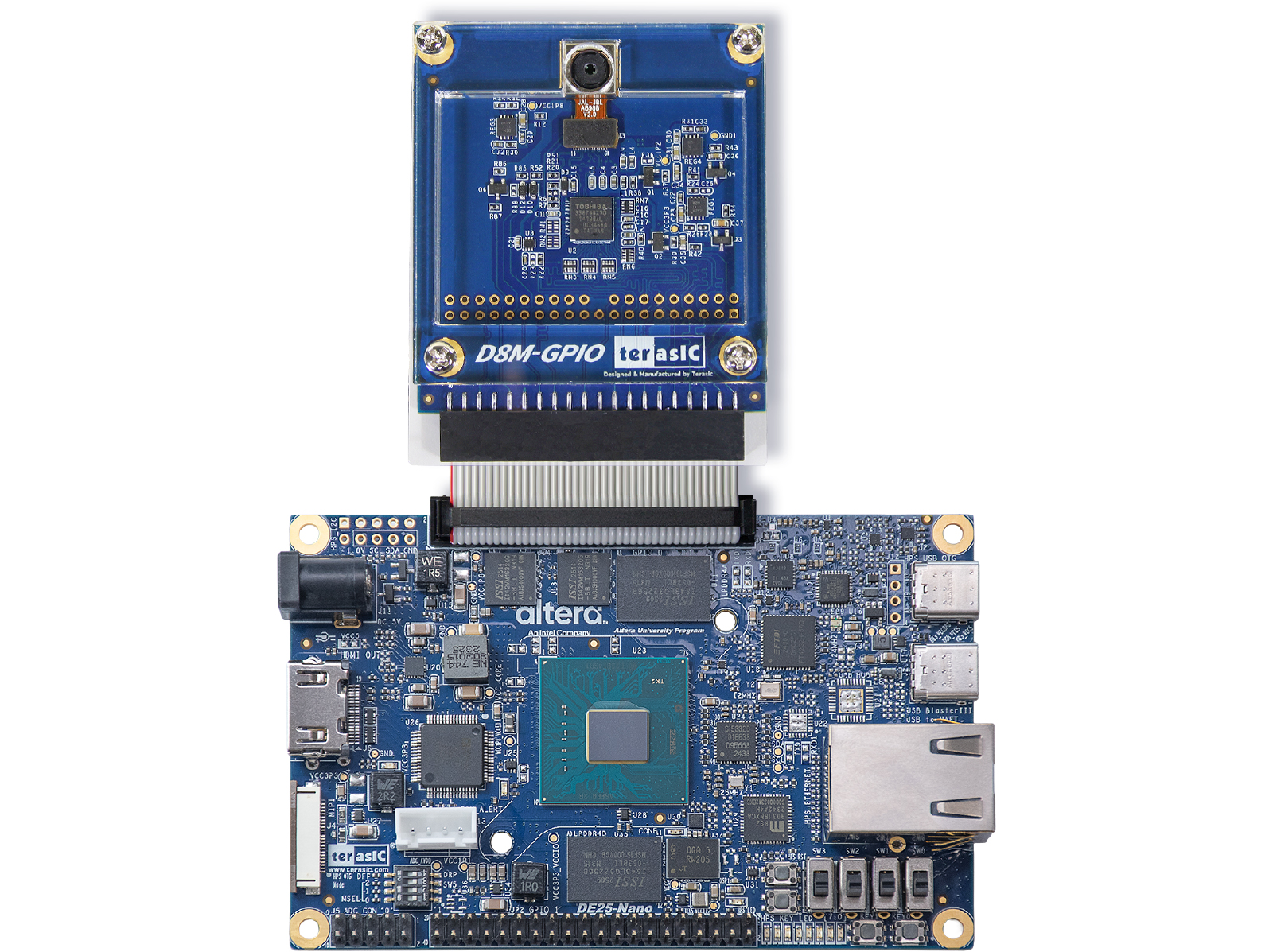

- Camera Interface: One MIPI connector with 2 data lanes

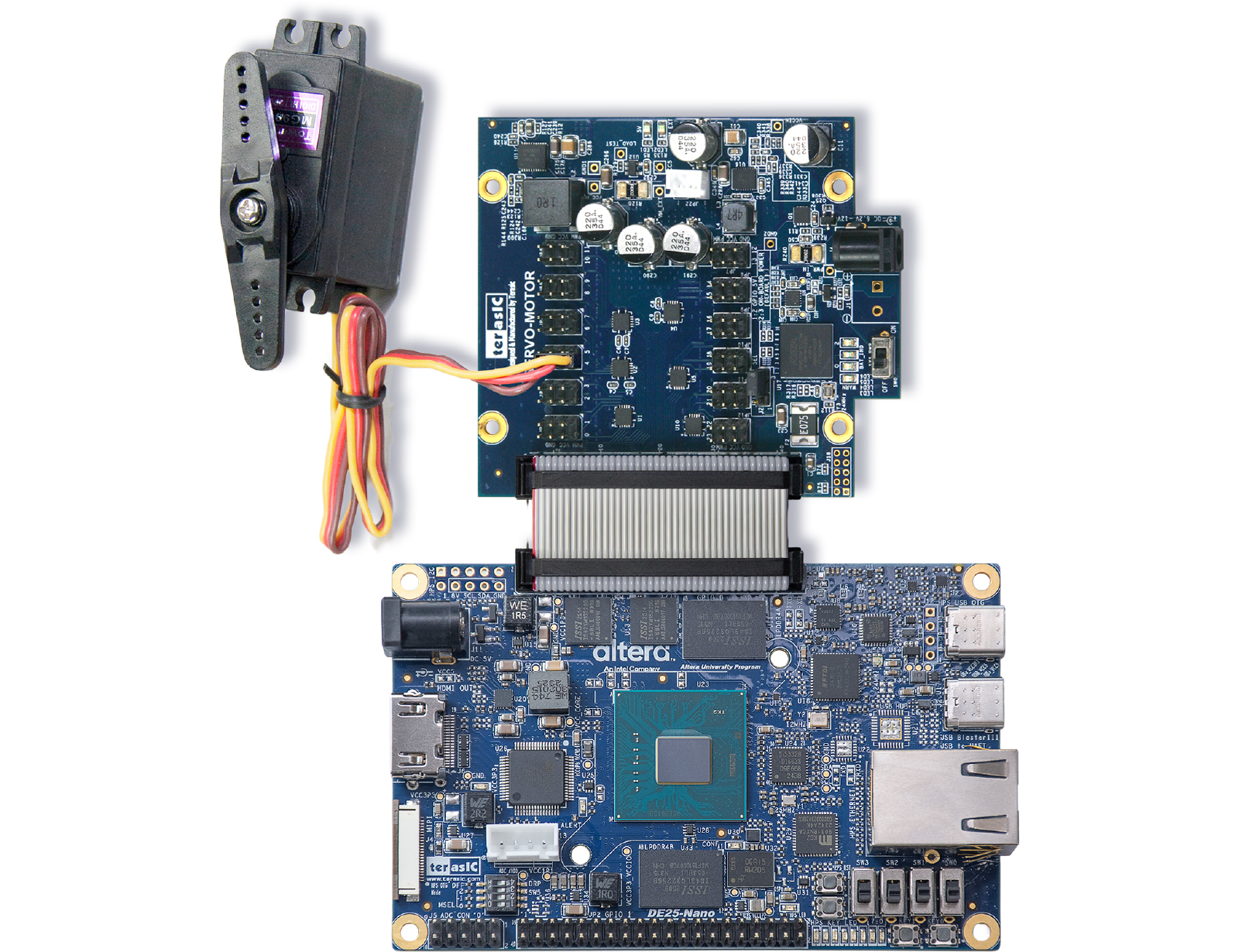

- ADC: 8-channel ADC with 2×5 header

- GPIO Headers: Two 3.3V 2×20 DE-GPIO headers

- User Interface: 8 user LEDs, 4 buttons, 4 slide switches

- UART Port: 2-pin UART via Type-C connector

- Thermal Management: Integrated temperature sensor and fan controller

HPS side

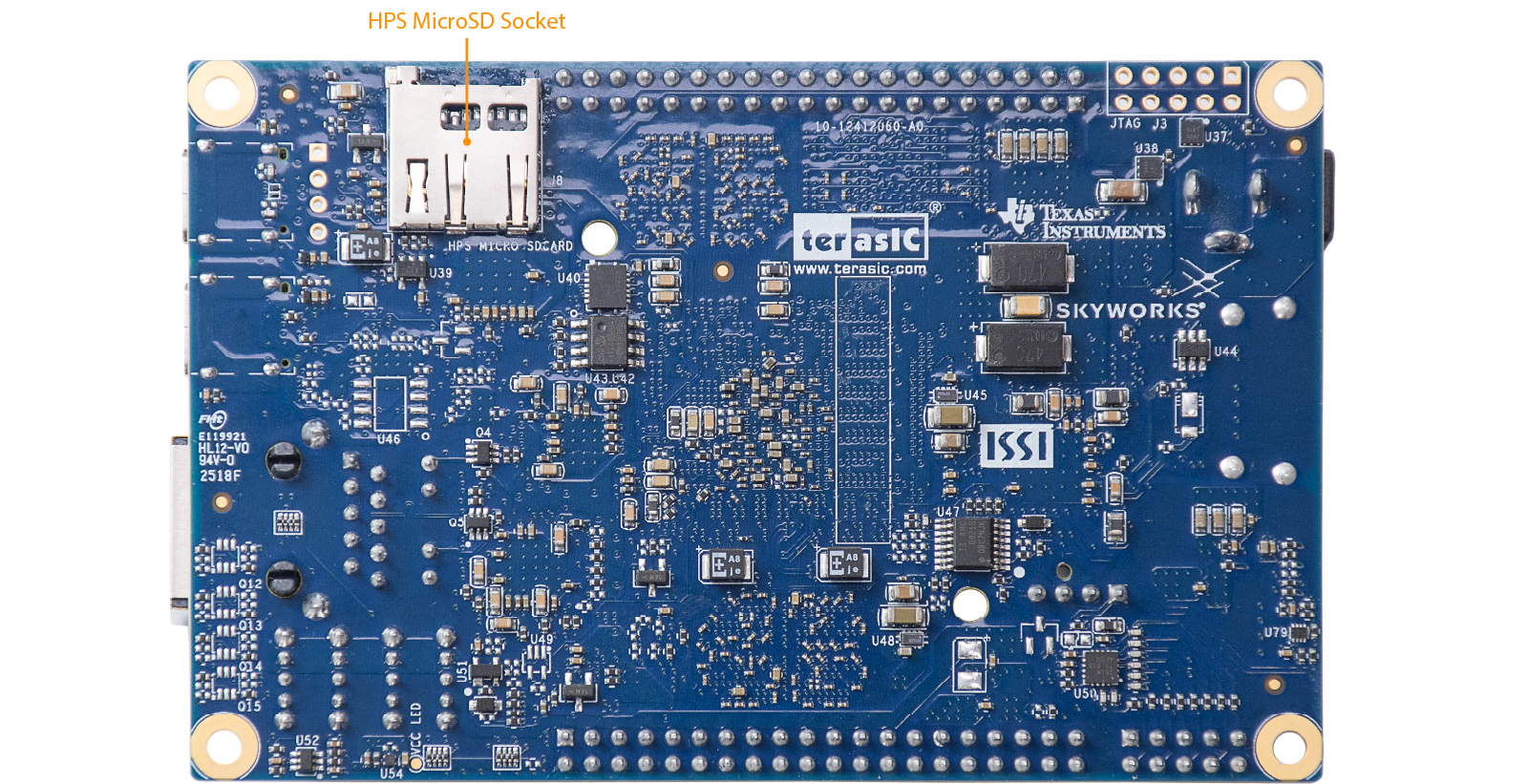

- MicroSD Socket

- LPDDR4 Memory: 1 GB LPDDR4 with 32-bit data bus (shared with FPGA). Data Rate: 2133 MT/s.

- Ethernet: Gigabit Ethernet PHY with RJ45 port

- USB Port: One USB 2.0 port via Type-C connector

- UART Interface: UART to USB via Type-C connector

- Sensor: Integrated accelerometer

- User Interface: 1 LED, 1 button, and 1 cold reset button

Software Support

- FPGA Example Code

- Linux BSP

Stay tuned to Metal Game Solid and the Pixel Cherry Ninja YouTube Channel to stay updated on this and all things FPGA Gaming.

A special thanks to David Shadoff for the heads up on this.

1 thought on “Potential MiSTer 1.5/Pro DE25-Nano Price Revealed”